| REV. | ZONE | ECN# | REVISION           | APPD | DATE    |

|------|------|------|--------------------|------|---------|

| Α    |      |      | PRODUCTION RELEASE | O.H. | 3/14/91 |

#### NOTE:

MANUFACTURERS RECEIVING APPLE APPROVED VENDOR STATUS FOR THEIR PRODUCT UNDER THIS PART NUMBER PLEASE NOTE: You must not change your part design, materials or manufacturing process from those used for the original samples submitted to and approved by Apple without written approval of Apple. Proposed changes determined by Apple to be significant, will require the manufacturer to submit new samples and/or data for review and approval prior to product shipments to Apple.

| $\bigcirc \oplus \ominus$                                                           | METRIC                                    |              |         | <b>≰</b> <sub>®</sub> Apple Computer, Inc.                                                                                                                                                                                                                                               |          |  |

|-------------------------------------------------------------------------------------|-------------------------------------------|--------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| DIMENSIONS ARE IN MILLIMETERS. DIMENSIONS IN BRACKETS ( ) ARE IN INCHES. TOLERANCES | B.T. 2/3/91                               | DESIGN CK    | 2/14/91 | NOTICE OF PROPRIETARY PROPERTY THE INFORMATION CONTAINED HEREIN IS THE PROPRIETA PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE POLLOWING: (i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE (ii) NOT TO REPRODUCE OR COPY IT (iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART |          |  |

| X.X ± 0.3 [.01]                                                                     | O.H. 2/44                                 | MFG APPD     | //      |                                                                                                                                                                                                                                                                                          |          |  |

| X.XX ± <u>0.13 [.005]</u>                                                           | QA APPD                                   | DESIGNER     | //      | IC, APPLE // OPTIO                                                                                                                                                                                                                                                                       | N CHIP.  |  |

| X.XXX ± 0.03 [.001]<br>ANGLEs ± 0.1                                                 | RELEASE //                                | scale:<br>NO | NE      | 128-PIN PQF                                                                                                                                                                                                                                                                              | •        |  |

| ANGLEs ± 0.1  or as noted  DO NOT SCALE DRAWING                                     | MATERIAL/FINISH<br>NOTED AS<br>APPLICABLE |              | A       | drawing number<br>343S0111-A                                                                                                                                                                                                                                                             | SHT 1/22 |  |

1.0 SCOPE: This specifies the parametric requirements for the Apple // Option Chip which provides the control circuitry and CPU host interface for the Apple // Emulation Card used by LC and possibly other future Macintosh computers.

It is implemented as a Gate-array using an LSI Logic Inc. LMA-9000 series 1.5 micron compacted-array in an 128-pin PQFP package.

The Apple // Option Chip provides support for all of the Apple //e functionality. This includes soft-switches, memory mapping, I/O card simulation, support for an external IWM and joystick port, and timing generation for an external 65C02. Apple //e video generation is not included because this function will be provided by software running on the Macintosh. The Apple // Option Chip provides an interface to the Macintosh so that the Apple //e functions can be monitored by software running on the Macintosh. When certain critical addresses are accessed by the 65C02, Apple // Option Chip captures the address and the data and temporarily halts the 65C02. A status flag to the Macintosh indicates that this "trap" has occured and the Macintosh can then read the address, data and other status information before allowing the 65C02 to continue. This process is used to capture all the video writes and most I/O accesses done by the 65C02 so that the Macintosh software can draw an appropriate Apple //e-like display on its screen.

The Apple // Option Chip supports 256K bytes of DRAM. This RAM is divided into a 128K byte space that represents the normal 128K Apple //e RAM, a 64K byte space that acts as an optional second 'Aux Bank' of Apple //e RAM, and a 64K byte space that acts like ROM and is partitioned into Apple ROM and I/O card ROM spaces. This ROM is normally writable from the Macintosh and not from the 65C02.

Since there is no ROM on card, Apple // Option Chip includes the capability of running from an external ROM or EPROM for burn-in testing. This external ROM is wired to the pins that would normally connect to the Macintosh address and data signals. When the external ROM is enabled, the trapping function described above is disabled and the 'ROM' areas of RAM are write-enabled so they can be tested by the 65C02.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE POLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

A

DRAWING NUMBER

343S0111-A

SCALE: NONE

SHT 3 OF 22

### **TABLE 1. PIN DESCRIPTION**

| 68020 CPU Bu | s Interface            |                               |         |

|--------------|------------------------|-------------------------------|---------|

| SIGNAL       | TYPE                   | DESCRIPTION                   | PIN #'S |

| ĀS           | input                  | CPU address strobe            | 31      |

| MRW          | input                  | CPU data bus direction        | 124     |

| MADDR(31)    | input                  | CPU upper address bits        | 37      |

| MADDR(27)    | input                  | CPU upper address bits        | 38      |

| MADDR(26)    | input                  | CPU upper address bits        | 39      |

| MADDR(25)    | input                  | CPU upper address bits        | 40      |

| MADDR(24)    | input                  | CPU upper address bits        | 41      |

| MADDR(23)    | input                  | CPU upper address bits        | 42      |

| MADDR(22)    | input                  | CPU upper address bits        | 43      |

| MADDR(21)    | input                  | CPU upper address bits        | 44      |

| MADDR(20)    | input                  | CPU upper address bits        | 45      |

| MADDR(4)     | input                  | CPU lower address bits        | 46      |

| MADDR(3)     | input                  | CPU lower address bits        | 47      |

| MADDR(2)     | input                  | CPU lower address bits        | 50      |

| MADDR(1)     | input                  | CPU lower address bits        | 51      |

| MADDR(0)     | input                  | CPU lower address bits        | 52      |

| MD(31)       | input/output - 8ma     | CPU Data bus upper word       | 7       |

| MD(30)       | input/output - 8ma     | CPU Data bus upper word       | 8       |

| MD(29)       | input/output - 8ma     | CPU Data bus upper word       | 9       |

| MD(28)       | input/output - 8ma     | CPU Data bus upper word       | 10      |

| MD(27)       | input/output - 8ma     | CPU Data bus upper word       | 12      |

| MD(26)       | input/output - 8ma     | CPU Data bus upper word       | 13      |

| MD(25)       | input/output - 8ma     | CPU Data bus upper word       | 14      |

| MD(24)       | input/output - 8ma     | CPU Data bus upper word       | 15      |

| MD(23)       | input/output - 8ma     | CPU Data bus upper word       | 19      |

| MD(22)       | input/output - 8ma     | CPU Data bus upper word       | 20      |

| MD(21)       | input/output - 8ma     | CPU Data bus upper word       | 21      |

| MD(20)       | input/output - 8ma     | CPU Data bus upper word       | 22      |

| MD(19)       | input/output - 8ma     | CPU Data bus upper word       | 25      |

| MD(18)       | input/output - 8ma     | CPU Data bus upper word       | 26      |

| MD(17)       | input/output - 8ma     | CPU Data bus upper word       | 27      |

| MD(16)       | input/output - 8ma     | CPU Data bus upper word       | 28      |

| FC(3)        | input                  | CPU function code             | 2       |

| FC(2)        | input                  | CPU function code             | 3       |

| FC(1)        | input                  | CPU function code             | 4       |

| FC(0)        | input                  | CPU function code             | 5       |

| DSACK0       | output(bidirect) - 4ma | CPU Data acknowledge: 8-bit   | 34      |

| DSACK1       | output(bidirect) - 4ma | CPU Data acknowledge: 16-bit  | 123     |

| SIZ(1)       | input                  | CPU transfer size code        | 29      |

| SIZ(0)       | input                  | CPU transfer size code        | 30      |

| CE           | input                  | Chip enable ROM enable select | 36      |

| LC           | input                  | Address decode mode control   | 122     |

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE POLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SIZE

DRAWING NUMBER

343S0111-A

SCALE: NONE

SHT 4

of 22

**TABLE 1. PIN DESCRIPTION (CONT)**

| SIGNAL        | TYPE         | DESCRIPTION                  | PIN #'S |

|---------------|--------------|------------------------------|---------|

| RA(8)         | output - 6ma | DRAM multiplexed address bus | 53      |

| RA(7)         | output - 6ma | DRAM multiplexed address bus | 54      |

| RA(6)         | output - 6ma | DRAM multiplexed address bus | 55      |

| RA(5)         | output - 6ma | DRAM multiplexed address bus | 56      |

| RA(4)         | output - 6ma | DRAM multiplexed address bus | 57      |

| RA(3)         | output - 6ma | DRAM multiplexed address bus | 58      |

| RA(2)         | output - 6ma | DRAM multiplexed address bus | 59      |

| RA(1)         | output - 6ma | DRAM multiplexed address bus | 60      |

| RA(0)         | output - 6ma | DRAM multiplexed address bus | 61      |

| RAS           | output - 6ma | DRAM row address strobe      | 63      |

| CAS           | output - 6ma | DRAM column address strobe   | 62      |

| <del>WP</del> | output - 6ma | DRAM write enable            | 66      |

| SIGNAL | TYPE               | DESCRIPTION                  | PIN #'S |

|--------|--------------------|------------------------------|---------|

| A(15)  | input              | 65C02 address bus            | 94      |

| A(14)  | input              | 65C02 address bus            | 95      |

| A(13)  | input              | 65C02 address bus            | 98      |

| A(12)  | input              | 65C02 address bus            | 99      |

| A(11)  | input              | 65C02 address bus            | 100     |

| A(10)  | input              | 65C02 address bus            | 101     |

| A(9)   | input              | 65C02 address bus            | 102     |

| A(8)   | input              | 65C02 address bus            | 103     |

| A(7)   | input              | 65C02 address bus            | 104     |

| A(6)   | input              | 65C02 address bus            | 105     |

| A(5)   | input              | 65C02 address bus            | 106     |

| A(4)   | input              | 65C02 address bus            | 107     |

| A(3)   | input              | 65C02 address bus            | 108     |

| A(2)   | input              | 65C02 address bus            | 109     |

| A(1)   | input              | 65C02 address bus            | 110     |

| A(0)   | input              | 65C02 address bus            | 111     |

| D(7)   | input/output - 6ma | 65C02 data bus               | 89      |

| D(6)   | input/output - 6ma | 65C02 data bus               | 88      |

| D(5)   | input/output - 6ma | 65C02 data bus               | 87      |

| D(4)   | input/output - 6ma | 65C02 data bus               | 86      |

| D(3)   | input/output - 6ma | 65C02 data bus               | 85      |

| D(2)   | input/output - 6ma | 65C02 data bus               | 84      |

| D(1)   | input/output - 6ma | 65C02 data bus               | 83      |

| D(0)   | input/output - 6ma | 65C02 data bus               | 82      |

| R/W    | input              | 65C02 data bus direction     | 92      |

| SYNC   | input              | 65C02 clock                  | 93      |

| PH0    | output - 4 ma      | 65C02 clock                  | 91      |

| RESET  | output - 4 ma      | 65C02 Reset                  | 73      |

| ĪRQ    | output - 4 ma      | 65C02 interrupt              | 74      |

| NMI    | output - 4 ma      | 65C02 non-maskable interrupt | 90      |

| BUFENB | output - 4 ma      | 65C02 bus buffer enable      | 72      |

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SIZE

DRAWING NUMBER

343S0111-A

SCALE: NONE

sht 5

of 22

**TABLE 1. PIN DESCRIPTION (CONT)**

| I/O and test functio                                                                               | ns                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| SIGNAL                                                                                             | TYPE                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   | PIN #'S                                                                                     |  |

| CLK7M Q3 IWMSEL SEL3.5 HDSEL C070STB XTRA BIT SPARESSW MUXIN SND ROMSEL PTO X1 X2 XCLK OUTENB XPOC | output - 4ma output - 4ma output - 4ma output - 8ma input output - 4ma output - 4ma output - 4ma output - 2ma output input input input input schmitt input | 7 MHz clock to IWM 2 MHz clock to IWM IWM select signal 3.5" drive select 3.5" drive head select Game port timer trigger Output port bit - Mac side Output port bit - 65C02 side Joystick mux output Apple //e spkr toggle output Chip enable for ext. config. ROM Input Threshold test output Xtal osc input Xtal osc output Main clock - 14MHz Disables all outputs when low Power-on-clear | 70<br>69<br>71<br>75<br>76<br>68<br>125<br>77<br>67<br>78<br>35<br>127<br>114<br>115<br>117 |  |

| TEST<br>XROM                                                                                       | input<br>input                                                                                                                                                                                                 | enables DSACK test mode<br>activates external ROM circuitry                                                                                                                                                                                                                                                                                                                                   | 120<br>121                                                                                  |  |

| Power                                                                                              | TYPE                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   | PIN#'S                                                                                      |  |

| V <sub>ss</sub>                                                                                    | power                                                                                                                                                                                                          | Pad-ring V <sub>SS</sub> - Gnd                                                                                                                                                                                                                                                                                                                                                                | 1, 11, 17, 23,<br>33, 48, 64,<br>80, 96, 113                                                |  |

| V <sub>SS2</sub>                                                                                   | power                                                                                                                                                                                                          | Core V <sub>SS</sub> - Gnd                                                                                                                                                                                                                                                                                                                                                                    | 18, 79, 118                                                                                 |  |

| V <sub>DD</sub>                                                                                    | power                                                                                                                                                                                                          | +5V                                                                                                                                                                                                                                                                                                                                                                                           | 16, 24, 32,<br>49, 65, 81,<br>97, 112, 128                                                  |  |

NOTICE OF PROPRIETARY PROPERTY NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE POLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SIZE

DRAWING NUMBER

343S0111-A

SCALE: NONE

**знт** 6

of 22

#### APPLICABLE DOCUMENTS (latest revision): 2.0

MIL-STD-202 Test methods for electronic and electrical component parts.

MIL-STD-883 Test methods and procedures for microelectronics.

#### 3.0 **REQUIREMENTS:**

- 3.1 PHYSICAL:

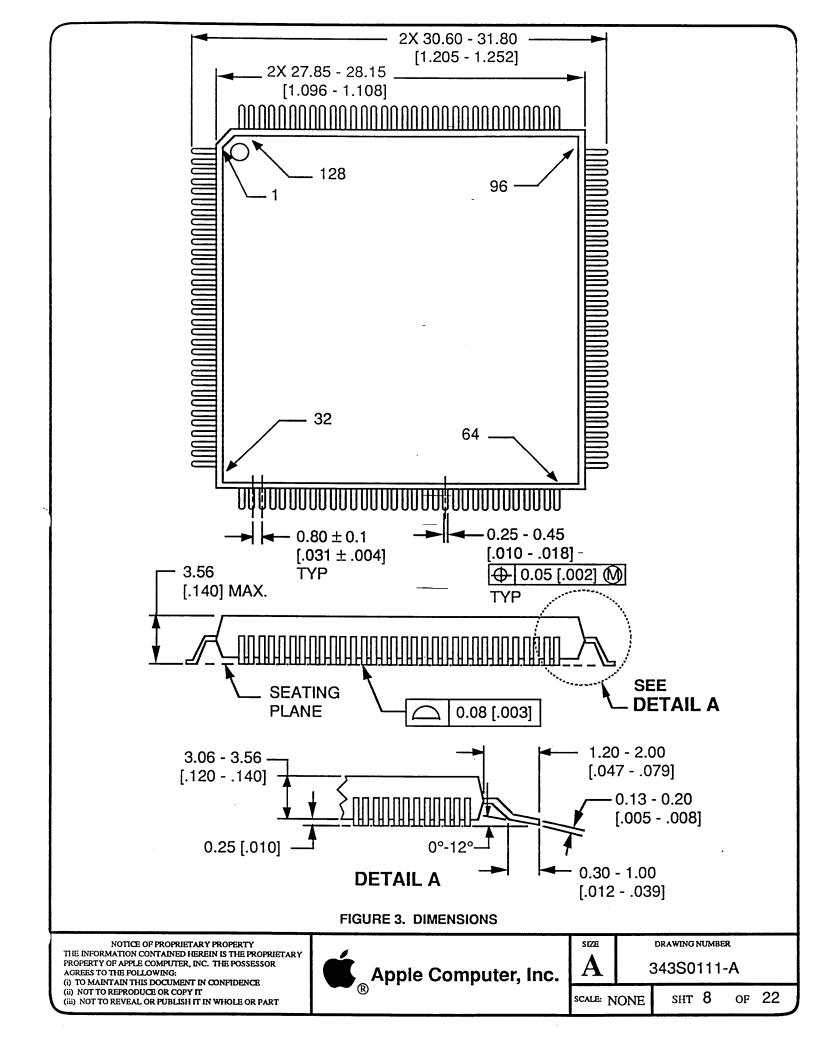

- PACKAGE: Void free plastic 128-pin PQFP package. Dimensions per Figure 3. 3.1.1

- 3.1.2 MARKINGS: Manufacturer's name or logo and manufacturing date code, Apple part number, current revision level, mask and copyright symbols, year and Apple name or logo.

EXAMPLE: 343S0111-A

(M)(C) 1990 Apple

- SOLDERABILITY: Leads solderability must meet MIL-STD-202, Method 208.

- 3.2 ELECTRICAL:

- 3.2.1 **ELECTROSTATIC DISCHARGE SENSITIVITY:** The minimum electrostatic discharge voltage per pin is ±2000 volts as specified in MIL-STD-883. method 3015.3 (i.e., C = 100 pF,  $R = 1.5 \text{K}\Omega$ ).

- LATCH-UP TEST: The minimum latch-up current for all pins except ground 3.2.2 is 50mA in both positive and negative directions. This applies to full temperature and power supply ranges.

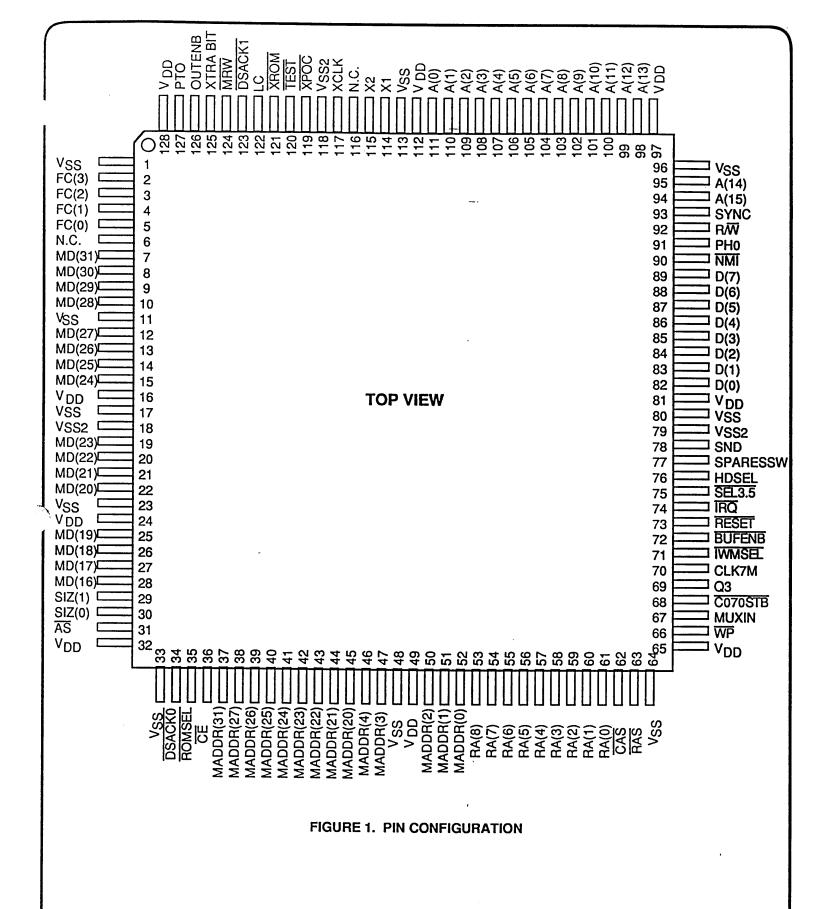

- 3.2.3 PIN CONFIGURATION: Per Figure 1.

- 3.2.4 PIN DESCRIPTION: Per Table 1.

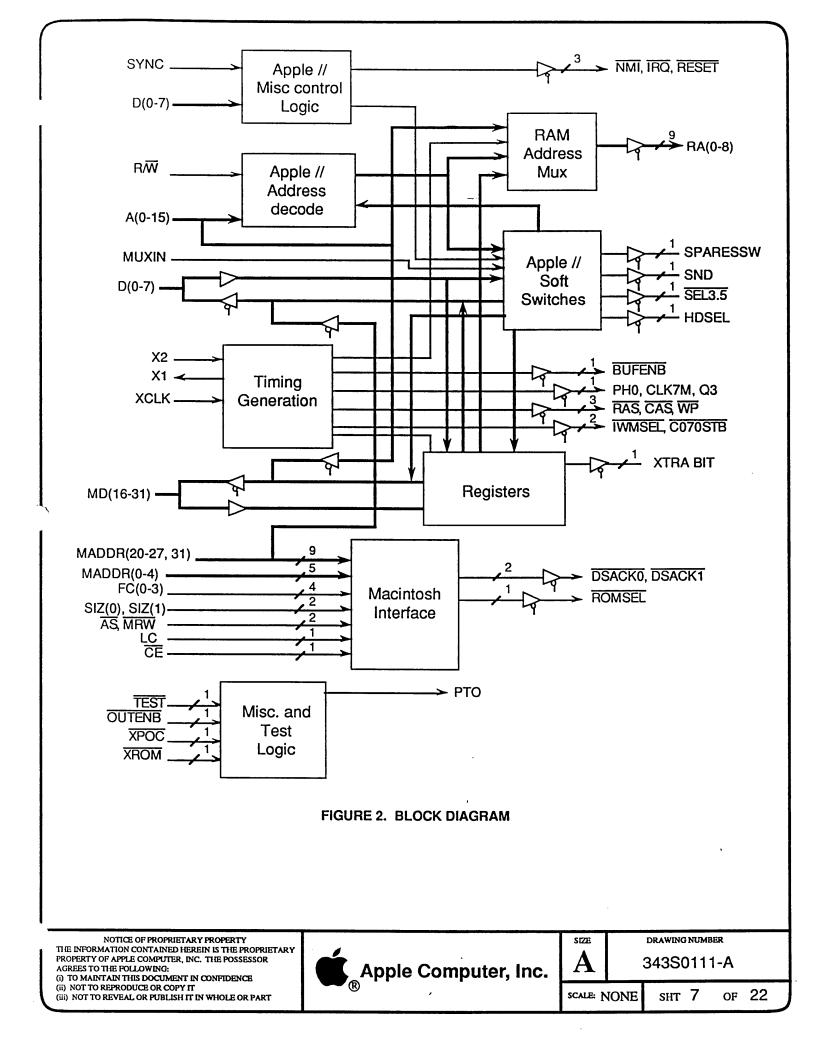

- 3.2.5 BLOCK DIAGRAM: Per Figure 2.

- ABSOLUTE MAXIMUM RATINGS: Per Table 2. 3.2.6

- 3.2.7 **RECOMMENDED OPERATING CONDITIONS:** Per Table 3.

- 3.2.8 STATIC PARAMETERS: Per Table 4.

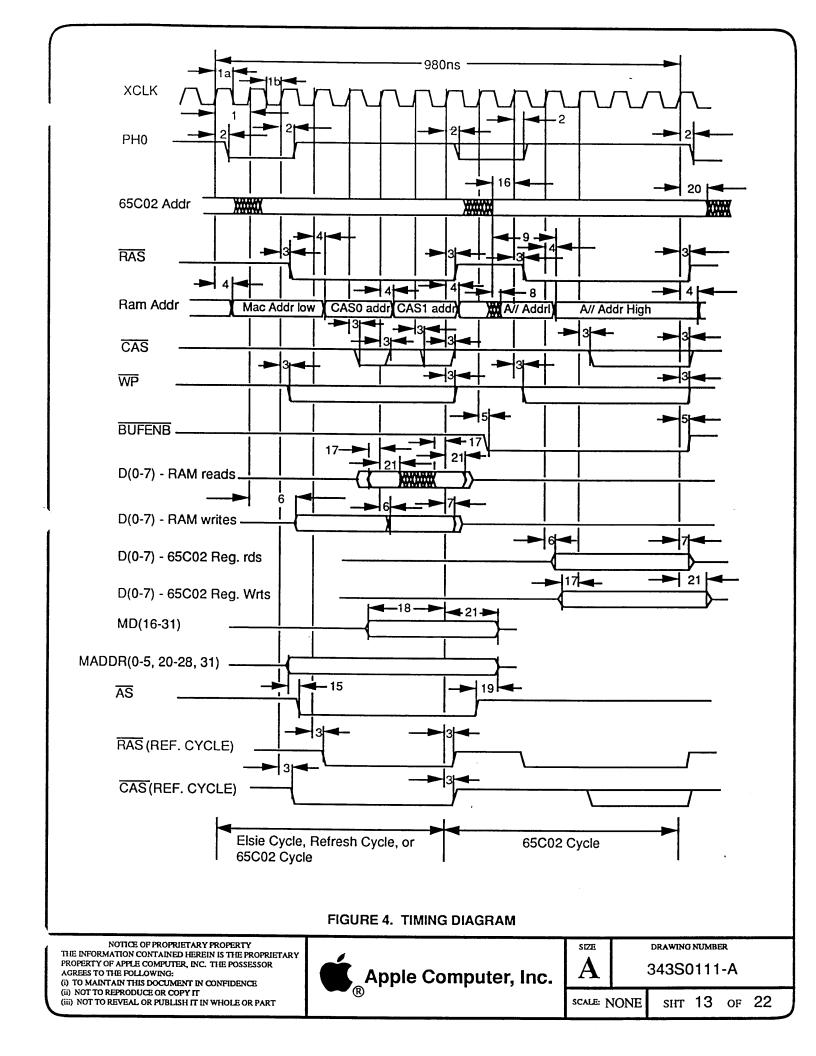

- 3.2.9 **DYNAMIC PARAMETERS:** Per Table 5, and Figure 4.

- 3.3 ENVIRONMENTAL:

- 3.3.1 RESISTANCE TO SOLDERING HEAT: 260°C for 10 sec in molten solder after 218°C for 30 sec in vapor phase, 60/40 solder and 260°C for 10 sec in molten solder after 240°C for 30 sec in I.R., 60/40 solder. Rate of temperature rise is 3°C/sec to within 100°C of the final temperature.

- 3.3.2 CLEANING: Parts must be washable in standard flux removal solvent and must not trap any cleaning liquids.

- 4.0 QUALITY ASSURANCE PROVISIONS: Parts shall be inspected to assure compliance to the requirements of this specification.

- PACKAGING: Parts shall be packaged according to requirements specified in purchase order for 5.0 safe delivery at Apple or Apple designated contractor. (Parts requiring Tape & Reel shall meet the proper Tape & Reel specification per the purchase order.)

22

OF

343S0111-A

**TABLE 2. ABSOLUTE MAXIMUM RATINGS**

| PARAMETER      | SYMBOL          | VALUE                           | UNIT |

|----------------|-----------------|---------------------------------|------|

| Supply Voltage | V <sub>DD</sub> | -0.3 to 7.0                     | V    |

| Input Voltage  | V <sub>IN</sub> | -0.3 to (V <sub>DD</sub> + 0.3) | ٧    |

| Operating Temp | TA              | 0 to 70                         | °C   |

| Storage Temp   | T <sub>S</sub>  | -40 to 125                      | °C   |

TABLE 3. RECOMMENDED OPERATING CONDITIONS

| PARAMETER      | SYMBOL          | VALUE    | UNIT |

|----------------|-----------------|----------|------|

| Supply Voltage | V <sub>DD</sub> | 5.0 ± 5% | V    |

| Input Voltage  | V <sub>IN</sub> | 0 to 5   | V    |

| Operating Temp | TA              | 0 to 70  | °C   |

**TABLE 4. STATIC PARAMETERS**

( $V_{DD}$  = 5.0V,  $V_{SS}$  = 0V,  $T_A$  = 0°C to +70°C, unless otherwise noted)

| PARAMETER                                                    | SYMBOL           | TEST CONDITION                                              | MIN | MAX | UNIT |

|--------------------------------------------------------------|------------------|-------------------------------------------------------------|-----|-----|------|

| Input high voltage<br>(Non-Schmitt inputs)                   | V <sub>IH</sub>  | V <sub>DD</sub> = 4.75 V                                    | 2.0 |     | ٧    |

| Input low voltage<br>(Non-Schmitt inputs)                    | V <sub>IL</sub>  | V <sub>DD</sub> = 5.25 V                                    |     | 0.8 | ٧    |

| Input hysterisis (Schmitt inputs - DSACKO, DSACK1, and XPOC) | V <sub>HST</sub> | V <sub>DD</sub> = 4.75 V                                    | 1.0 | 1.5 | V    |

| Input buffer leakage                                         | I <sub>IN</sub>  | $V_{IN} = 0$ to $V_{DD}'$ ,<br>$V_{DD} = 5.25$ V            | -10 | +10 | μА   |

| Output buffer leakage (when tristated)                       | l <sub>oz</sub>  | $V_{OUT} = 0 \text{ to } V_{DD},$ $V_{DD} = 5.25 \text{ V}$ | -10 | +10 | μА   |

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SCALE: NONE SHT 10 OF 22

## TABLE 4. STATIC PARAMETERS (CONT)

( $V_{DD}$  = 5.0V,  $V_{SS}$  = 0V,  $T_A$  = 0°C to +70°C, unless otherwise noted)

| PARAMETER                         | SYMBOL           | TEST CONDITION                                       | MIN | MAX | UNIT |

|-----------------------------------|------------------|------------------------------------------------------|-----|-----|------|

| Output voltage<br>(16 mA outputs) | V <sub>OL</sub>  | I <sub>OL</sub> = -16 mA<br>V <sub>DD</sub> = 4.75 V |     | 0.4 | V    |

| Output voltage<br>(8 mA outputs)  | V <sub>OL</sub>  | I <sub>OL</sub> = -8 mA<br>V <sub>DD</sub> = 4.75 V  |     | 0.4 | V    |

| Output voltage<br>(4 mA outputs)  | V <sub>OL</sub>  | I <sub>OL</sub> = -4 mA<br>V <sub>DD</sub> = 4.75 V  |     | 0.4 | V    |

| Output voltage<br>(2 mA outputs)  | V <sub>OL</sub>  | I <sub>OL</sub> = -2 mA<br>V <sub>DD</sub> = 4.75 V  |     | 0.4 | V    |

| Output voltage                    | V <sub>OH</sub>  | I <sub>OL</sub> = 16 mA                              | 2.4 |     | V    |

| (16 mA outputs)                   |                  | I <sub>OL</sub> = 8 mA<br>V <sub>DD</sub> = 4.75 V   | 3.5 |     | V    |

| Output voltage                    | V <sub>OH</sub>  | I <sub>OL</sub> = 8 mA                               | 2.4 |     | ٧    |

| (8 mA outputs)                    |                  | l <sub>OL</sub> = 4 mA<br>V <sub>DD</sub> = 4.75 V   | 3.5 |     | V    |

| Output voltage                    | V <sub>OH</sub>  | I <sub>OL</sub> = 4 mA                               | 2.4 |     | ٧    |

| (4 mA outputs)                    |                  | I <sub>OL</sub> = 12 mA<br>V <sub>DD</sub> = 4.75 V  | 3.5 |     | V    |

| Output voltage                    | V <sub>OH</sub>  | I <sub>OL</sub> = 2 mA                               | 2.4 |     | ٧    |

| (2 mA outputs)                    |                  | I <sub>OL</sub> = 1 mA<br>V <sub>DD</sub> = 4.75 V   | 3.5 |     | ٧    |

| Input Capacitance                 | C <sub>IN</sub>  | V <sub>IN</sub> =0, T <sub>A</sub> =25°C, f=1 MHz    |     | 10  | pF   |

| Output Capacitance                | C <sub>TS</sub>  | V <sub>OUT</sub> =0, T <sub>A</sub> =25°C, f=1 MHz   |     | 10  | pF   |

| Supply current (No load)          | Icc              | Clock = 14MHz                                        |     | 25  | mA   |

| Standby Current                   | I <sub>SBY</sub> | Outputs unloaded.<br>Clock = 0 MHz                   |     | 10  | μА   |

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR (i) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SIZE

DRAWING NUMBER 343S0111-A

SCALE: NONE

SHT 11 OF 22

#### **TABLE 5. DYNAMIC PARAMETERS**

$(V_{DD} = 5.0V, V_{SS} = 0V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \text{ unless otherwise noted})$

| A.C. P                                                                              | A.C. PARAMETERS                                                                                                                                         |                                                                                                                                                                                                                                           |                |                     |                                         |                                                                                 |                                                     |                                      |  |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|-----------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------|--|

| NO.                                                                                 | INPUT                                                                                                                                                   | то оитрит                                                                                                                                                                                                                                 | MĪN            | TYP                 | MAX                                     | UNIT                                                                            | LOAD (pF)                                           | NOTES                                |  |

| 1<br>1a<br>1b<br>1c<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | Clock period Clock high period Clock low period Clock Rise/Fall time Clock Clock Clock Clock Clock Clock A(0-15) A(0-15) A(0-15) A(0-15) A(0-15) Outenb | - n/a n/a n/a n/a n/a n/a - PH0 RAS, CAS, WP RA(0-8) Gen. Clk'd outputs D(0-7) (turn on or chg.) D(0-7) Hi-Z  RA(0-8) when RAS active RA(0-8) when CAS active MD(16-31) A2 Decoded outputs  D(0-7) MD(16-31) Hi-Z  All disablable outputs | 65<br>25<br>25 | 70<br>35<br>35<br>5 | % % 10 20 25 35 40 30 40 25 30 25 15 30 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>n | 35<br>50<br>50<br>50<br>50<br>50<br>50<br>100<br>50 | 1.<br>2.<br>2.<br>3., 4.<br>6.<br>6. |  |

### A.C. OPERATING CONDITIONS - INPUT SETUP TIME REQUIREMENTS

| NO.                  | INPUT SETUP                                                    | RELATIVE TO INPUT                                                     | MIN | ТҮР | MAX                 | UNIT                 | LOAD (pF) | NOTES |

|----------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|---------------------|----------------------|-----------|-------|

| 15<br>16<br>17<br>18 | Mac Addrs. Inputs<br>65C02 addrs inputs<br>D(0-7)<br>MD(16-31) | AS falling edge Clock rising edge Clock rising edge Clock rising edge |     |     | 0<br>35<br>13<br>10 | ns<br>ns<br>ns<br>ns |           | 5.    |

# A.C. OPERATING CONDITIONS - INPUT HOLD TIME REQUIREMENTS

| NO.            | INPUT HOLD                                                   | RELATIVE TO INPUT                                  | MIN          | ТҮР | MAX | UNIT           | LOAD (pF) | NOTES |

|----------------|--------------------------------------------------------------|----------------------------------------------------|--------------|-----|-----|----------------|-----------|-------|

| 19<br>20<br>21 | Mac Addrs. Inputs<br>65C02 addrs inputs<br>D(0-7), MD(16-31) | AS rising edge Clock rising edge Clock rising edge | 10<br>5<br>5 | ,   |     | ns<br>ns<br>ns |           | 5.    |

#### NOTES:

1. General clocked outputs are: SND, IRQ, NMI, RESET, BUFENB, WP, DSACKO, DSACK1, CLK7M, Q3,

C070STB, SEL3.5, HDSEL, XTRA BIT, SPARESSW,

2. A2 decoded outputs are: IWMSEL, C070STB,

3. Mac addrs inputs are: SIZ(0), SIZ(1), FC(0-3), MADDR(0-4), MADDR(20-27), MADDR(31)

4. 65C02 Addrs inputs are: A(0-15), R/W, SYNC

5. Setup times for 65C02 addrs inputs are setups to the relevant clock edge.

6. Used for factory testing only.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

DRAWING NUMBER

343S0111-A

SCALE: NONE

SHT 12 OF 22

- 6.0 SUPPLEMENTARY INFORMATION: The following is not to be used for the acceptance or rejection of the part herein.

- 6.1 OPERATIONAL DESCRIPTION:

- 6.1.1 MACINTOSH VIEW OF APPLE // EMULATION CARD:

Apple // Emulation Card looks as much as possible like an Apple //e to the 65C02 microprocessor and looks like a set of I/O registers to the Macintosh.

| <u>Rea</u>  | <u>d</u>   | <u>Address</u> | Write           | <u> </u>   |  |  |

|-------------|------------|----------------|-----------------|------------|--|--|

| MS Byte     | LS Byte    |                | MS Byte         | LS Byte    |  |  |

| Trap/Dis    | spatch     | \$xxx0         | - Unused -      | - Unused - |  |  |

| A// Trap Ad | dress      | \$xxx4         | - Unused -      | - Unused - |  |  |

| A// Soft-Sw | itches     | \$xxx8         | - Unused -      | - Unused - |  |  |

| Trap Data   | Alt. Cntrl | \$xxxC         | Go-Ahead        | Alt Cntrl. |  |  |

| A// Memo    | ry Data    | \$xx10         | A// Memory Data |            |  |  |

| - Unused -  | - Unused - | \$xx14         | - Unused -      | - Unused - |  |  |

| Kbd Data    | Rep Data   | \$xx18         | Kbd Data        | Rep Data   |  |  |

| A// Addi    | Cntr/Reg   | \$xx1C         | A// Addr Cn     | tr/Reg     |  |  |

| Control     | Reg.       | \$xx20         | Contro          | l Reg.     |  |  |

|             |            | _              |                 |            |  |  |

Indicates currently unused.

Indicates register supported for test purposes

FIGURE 5. APPLE // OPTION CHIP REGISTER MAP

#### NOTE:

7. The addresses shown above are offsets from the LC or other Macintosh I/O slot base address. When the 65C02 accesses certain key I/O locations or writes to the Apple I/e display areas, it is "Trapped" (or halted temporarily) and the address accessed and data read or written is latched so that the information is available to the Macintosh. After the Macintosh has gathered the data, it accesses the "GoAhead" location or writes to the Read Data Replacement register to allow the 65C02 to continue. The Apple I/Emulation Card also provides a "Hint" mode which can be enabled in place of traps for 65C02 video writes. Traps are disabled when the Disk Motor-On switch is true, so that code accessing the IWM chip will not be disturbed. Hint mode captures the address and data written, but does not halt the 65C02. The current hint is cleared when the Macintosh reads the Trap Address register further below.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

### 6.1.2 THE TRAP/DISPATCH/STATUS REGISTER:

Read only Addr: Base + xxxx0 Size: 16-bits

This register provides information describing the type of trap that has occured. It reads zero when 65C02 is not trapped. When non-zero, the value in the register may be used directly to index into a table of long addresses to vector quickly to the appropriate trap handler. The Trap/dispatch codes are provided in the lower byte only.

TABLE 6. TRAP/DISPATCH REGISTER CODES

| TRAP TYPE               | DISPATCH CODE                         | TRAP TYPE               | DISPATCH CODE                         |  |  |

|-------------------------|---------------------------------------|-------------------------|---------------------------------------|--|--|

| No Trap                 | d¹dº 000 000                          | Soft-Sw Write           | d¹dº 100 000                          |  |  |

| ** unassigned           | d¹dº 000 001                          | Soft-Sw Read            | d¹dº 100 001                          |  |  |

| Txt Wr. main Pgl Trp    | d¹d° 000 010                          | Txt Wr. main PG2 Trp    | d¹dº 100 010                          |  |  |

| Txt Wr. main Pgl Hint   | d¹d° 000 011                          | Txt Wr. main PG2 Hint   | d¹dº 100 011                          |  |  |

| HiRes Wr. main Pgl Trap | d¹d° 000 100                          | HiRes Wr. main Pg2 Trap | d¹dº 100 100                          |  |  |

| HiRes Wr. main Pg1 Hint | d¹d° 000 101                          | HiRes Wr. main Pg2 Hint | d¹dº 100 101                          |  |  |

| ** unassigned           | d¹d° 000 110                          | ** unassigned           | d¹dº 100 110                          |  |  |

| ** unassigned           | d¹dº 000 111                          | ** unassigned           | d¹dº 100 111                          |  |  |

| I/O Slot Hdw. write     | d¹dº 001 000                          | \$C0E8 Write            | d¹dº 101 000                          |  |  |

| I/O slot Hdw. read      | d¹d° 001 001                          | \$C0E8 Read             | d <sup>1</sup> d <sup>0</sup> 101 001 |  |  |

| Text Wr. Aux Pgl Trap   | d¹d° 001 010                          | Txt Wr. aux Pg2 Trp     | d¹dº 101 010                          |  |  |

| Text Wr. Aux Pg1 Hint   | d <sup>1</sup> d <sup>0</sup> 001 011 | Txt Wr. aux Pg2 Hint    | d¹dº 101 011                          |  |  |

| HiRes Wr. Aux Pg1 Trap  | d <sup>1</sup> d <sup>0</sup> 001 100 | HiRes Wr. aux Pg2 Trap  |                                       |  |  |

| HiRes Wr. Aux Pgl Hint  | d <sup>1</sup> d <sup>0</sup> 001 101 | HiRes Wr. aux Pg2 Hint  | d¹dº 101 101                          |  |  |

| ** unassigned           | d <sup>1</sup> d <sup>0</sup> 001 110 | ** unassigned           | d <sup>1</sup> d <sup>0</sup> 101 110 |  |  |

| ** unassigned           | d <sup>1</sup> d <sup>0</sup> 001 111 | ** unassigned           | d¹dº 101 111                          |  |  |

| S0 \$C8-Space write     | d¹dº 010 000                          | ** unassigned           | d¹dº 110 000                          |  |  |

| S0 \$C8-Space Read      | d <sup>1</sup> d <sup>0</sup> 010 001 | ** unassigned           | d¹d° 110 001                          |  |  |

| S2 \$C8-Space write     | d <sup>1</sup> d <sup>0</sup> 010 010 | ** unassigned           | d¹dº 110 010                          |  |  |

| S2 \$C8-Space Read      | d¹d° 010 011                          | ** unassigned           | d¹dº 110 011                          |  |  |

| S4 \$C8-Space write     | d¹dº 010 100                          | ** unassigned           | d¹dº 110 100                          |  |  |

| S4 \$C8-Space Read      | d¹d° 010 101                          | ** unassigned           | d <sup>1</sup> d <sup>0</sup> 110 101 |  |  |

| S6 \$C8-Space write     | d <sup>1</sup> d <sup>0</sup> 010 110 | ** unassigned           | d <sup>1</sup> d <sup>0</sup> 110 110 |  |  |

| S6 \$C8-Space Read      | d¹dº 010 111                          | ** unassigned           | d¹dº 110 111                          |  |  |

| S1 \$C8-Space write     | d¹d° 011 000                          | \$C0E9 Write            | d¹dº 111 000                          |  |  |

| S1 \$C8-Space Read      | d¹d0 011 001                          | \$C0E9 Read             | d¹dº 111 001                          |  |  |

| S3 \$C8-Space write     | d¹d° 011 010                          | ** unassigned           | d¹dº 111 010                          |  |  |

| S3 \$C8-Space Read      | d¹d° 011 011                          | ** unassigned           | d¹dº 111 011                          |  |  |

| S5 \$C8-Space write     | d¹d° 011 100                          | ** unassigned           | d¹dº 111 100                          |  |  |

| S5 \$C8-Space Read      | d¹d° 011 101                          | ** unassigned           | d¹dº 111 101                          |  |  |

| S7 \$C8-Space write     | d <sup>1</sup> d <sup>0</sup> 011 110 | ** unassigned           | d¹dº 111 110                          |  |  |

| S7 \$C8-Space Read      | d¹d° 011 111                          | ** unassigned           | d¹dº 111 111                          |  |  |

#### NOTE:

8. d¹ and d⁰ are two bits in the Alt Control Register that can be used by the programmer to select one of four dispatch tables.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

| SIZE | DRAWING NUMBER |

|------|----------------|

| A    | 343S0111-A     |

## TABLE 7. TRAPPED APPLE //e ACCESSES

| Display Areas:                                                                                                   |                                                     |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ADDRESS                                                                                                          | R/W                                                 | DESCRIPTION                                                                                                                                                                                                                     | COMMENTS                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| \$400-7FF<br>\$800-BFF<br>\$2000-3FFF<br>\$4000-5FFF                                                             | Write<br>Write<br>Write<br>Write                    | Text/LoRes pg1 stores Text/LoRes pg2 stores HiRes/Dbl-Hires pg1 stores HiRes/Dbl-Hires pg2 stores  Areas:                                                                                                                       | Maskable for main/aux<br>Maskable for main/aux<br>Maskable for main/aux<br>Maskable for main/aux                                                                                                                                                                                                                      |  |  |  |  |  |

| ADDRESS                                                                                                          | R/W                                                 | DESCRIPTION                                                                                                                                                                                                                     | COMMENTS                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| \$C000,1<br>\$C00C-D<br>\$C00E-F<br>\$C040-F<br>\$C050-57<br>\$C058-5F<br>\$C060-67<br>\$C070-7F                 | Write<br>Write<br>Write<br>R/W<br>R/W<br>R/W<br>R/W | 80Store Soft-sw 80Col soft-sw AltCharSet soft-sw Spare Soft-switch area Display soft-sw's Announciators Joy-Stick Pdls & Swtchs. JoyStick Trig and spares                                                                       | Non-maskable - Affects display Non-maskable - Affects display Non-maskable - Affects display Non-maskable Non-maskable - Affects display Non-maskable - AN3 Affects display Maskable Non-maskable                                                                                                                     |  |  |  |  |  |

| ADDRESS                                                                                                          | R/W                                                 | DESCRIPTION                                                                                                                                                                                                                     | COMMENTS                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| \$C090-9F<br>\$C0A0-AF<br>\$C0B0-BF<br>\$C0C0-CF<br>\$C0D0-DF<br>\$C0E8-E9<br>\$C0F0-FF<br>\$C800-CFFE<br>\$CFFF | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W       | Slot 1 Hardware accesses Slot 2 Hardware accesses Slot 3 Hardware accesses Slot 4 Hardware accesses Slot 5 Hardware accesses Slot 6 Motor on/off switch Slot 7 Hardware accesses Shared 2K \$C8-Space Shared \$C8-Space switch. | Non-maskable - For card simulation Non-maskable - 5.25" Motor on/off Non-maskable - For card simulation Maskable - For card simulation Non-maskable - For card simulation |  |  |  |  |  |

#### NOTES:

- 9. The "Screen-Hole" areas in the above address ranges do not trap. These are the \$xx78-7F and \$xxF8-FF address ranges in the display areas.

- 10. Display writes do not trap when the Slot 6 motor switch is 'on'.

- 11. Display writes may optionally cause 'hints' instead of traps if Hint mode is enabled in the Apple // Emulation Card Control register.

- 12. \$CFFF accesses produce \$C8-Space dispatch codes in the trap dispatch register. The dispatch code will indicate which slot ROM space was most recently accessed before the \$C8-Space access occured.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE POLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

A 343

DRAWING NUMBER 343S0111-A

SCALE: NONE

SHT 16 OF 22

#### 6.1.3 THE TRAP REGISTER:

Read only Addr: Base + xxxx4 Size: 16-bits

Bits 0-7: The L.S. byte of the Apple //e address trapped. Bits 8-15: The M.S. byte of the Apple //e address trapped.

Reading a byte from addr B+xxx4 will provide the high byte of the Apple // trap address.

Reading a byte from addr B+xxx5 will provide the low byte of the Apple // trap address.

#### NOTES:

- 13. The data in this register will only be valid and stable while the Apple // is trapped or stopped, or when the hint flag in the Apple // Emulation Card Control Register is set.

- 14. This register only provides the 16-bit 65C02 address that was present when the trap occured. It does not indicate whether the 65C02 was accessing the main 64K or aux 64K RAM bank, however the Main/Aux information is implicit in the Trap/Dispatch code generated.

#### 6.1.4 THE SOFT-SWITCH REGISTER

Read only Addr: Base + xxxx8 Size: 16-bits

This register allows the LC software to read the state of the Apple //e soft-switches.

| BIT | DESCRIPTION   | BIT | DESCRIPTION  |

|-----|---------------|-----|--------------|

| 15  | AltCharSet-Sw | 7   | KbdFlg       |

| 14  | Text Sw       | 6   | An1 Sw       |

| 13  | Hi-Res Sw     | 5   | An0 Sw       |

| 12  | AN3 Sw        | 4   | SlotC3ROM Sw |

| 11  | 80COI Sw      | 3   | IntCxROM Sw  |

| 10  | Mixed Sw      | 2   | AltZP Sw     |

| 9   | Page2 Sw      | 1   | RAMWrt Sw    |

| 8   | 80Store Sw    | 0   | RAMRd Sw     |

Reading a byte from addr B+xxx8 will provide the high byte of the Apple // soft-switch status.

Reading a byte from addr B+xxx9 will provide the low byte of the Apple // soft-switch status.

#### 6.1.5 THE TRAP DATA REGISTER

Read only Addr: Base + xxxxC Size: 8-bits

Bits 0-7: The byte of the Apple //e data being read or written when the Apple // trapped.

#### NOTE:

15. The data in this register is only valid when the Apple // is trapped or stopped or when the Hint Flag in the Apple // Emulation Card Control Register is set.

### 6.1.6 THE ALT. CONTROL REGISTER

Read/Write Addr: Base + xxxxD Size: 8-bits

This register allows the LC to control various aspects of the Apple // Emulation Card card operation. There is an additional 16-bit control register at loc \$B+xxx20.

Reads are supported to facilitate testing and simply return the last value written.

#### **BIT DESCRIPTION**

- 7 AKD Any-Key-Down signal to Apple II side.

- 6 VBL signal to 65C02 programs

- 5 Enable alternate 65C02 16K byte DarkSide ROM bank

- 4 Enable ROM writes from 65C02.

- 3 Select Hi bank 128K RAM bank for read/write access

- 2 Enable alternate 64K Apple II Aux Bank.

- 1 D1

- 0 D0

#### NOTE:

16. Bits 1 and 0 are the d¹do bits used in Table 6.

### 6.1.7 THE MEMORY DATA REGISTER

Read/Write Addr: Base + xxx10 Size: 16-bits

This register or used to read or write the Apple // RAM. Bits 0-7 read/write the Aux 64K bank of RAM and bits 8-15 read/write the Main 64K bank. Each time this register is accessed, the pointer address stored in the RAM Address latch/counter register is incremented, so that contiguous blocks of data can be moved to or from the Apple // RAM with a series of sequential read or writes to the Memory data register.

### 6.1.8 THE KEYBOARD DATA REGISTER

Read/Write Addr: Base + xxx18 Size: 8-bits

Bit 7: - Unused -

Bits 0-6: 7 bits of simulated Apple //e ASCII keyboard data.

Writes to this register simulate keystrokes on the Apple // keyboard. When a key on the LC keyboard is pressed, the equivalent ASCII data should be written to this register as soon as possible, and the Bit 7 should be written a 'one' as long as any key is held down, and changed to a 'zero' when the key is released.

The Apple // keyboard data flag is handled automatically by the logic in the Apple // Emulation Card gate-array. It will be set when data is written to the register, and cleared when the Apple // software accesses the proper soft-switch location(s) to clear the flag.

Reading back from this register is supported to facilitate testing.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING:

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

Apple Computer, Inc.

A

DRAWING NUMBER

343S0111-A

SCALE: NONE

SHT 18 OF 22

### 6.1.9 THE READ DATA REPLACEMENT REGISTER - WRITE ONLY

Read/Write Addr: Base + xxx19 Size: 8-bits

This register allows the LC software to optionally replace the data that the Apple // would have read from a trapped address. For example, if the Apple // Emulation Card was trying to read from a hardware location on an I/O card, the LC could make it look to the Apple // Emulation Card like the hardware was present by supplying the appropriate data.

Reading back from this register is supported to facilitate testing.

Bits 0-7: 8 bits of data to optionally replace the data read during a trapped Apple //e read.

#### NOTE:

17. Writes to this register will be ignored unless the Apple // Emulation Card is currently trapped and in a read state. However, to avoid the possibility of a trap occuring at the same time the data is being written to the register, it should not normally be written to unless the Apple // Emulation Card is currently trapped.

Writes to this register automatically issue a "Go-Ahead" for the current trap and allow the 65C02 to continue running.

### 6.1.10 THE APPLE // ADDRESS LATCH / COUNTER REGISTER

Read-only Addr: Base + xxx1C Size: 16-bits

This register is actually a 16-bit counter that can be loaded by the LC software and used to address the Apple // Emulation Card memory when LC accesses it. Each time LC accesses the Apple //e memory the counter is automatically incremented.

Reading back from this location will return the current value in the Counter and is supported primarily to facilitate testing.

Bits 8-15: (Addr xx1C): Apple //e addresses 8-15 - The MS byte Bits 0-7: (Addr xx1D): Apple //e addresses 0-7 - The LS byte.

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

## 6.1.11 THE APPLE // EMULATION CARD CONTROL REGISTER

Read-only Addr: Base + xxx20 Size: 16-bits

This register provides a mechanism so that the LC software can control various aspects of the Apple // Emulation Card hardware.

| BIT | DESCRIPTION            | BIT | DESCRIPTION                       |

|-----|------------------------|-----|-----------------------------------|

| 15  | RESET to D.E.          | 7   | Hires Pg1 trap enb.               |

| 14  | NMI to D.E.            | 6   | Hires pg2 trap enb.               |

| 13  | IRQ to D.E.            | 5   | TxtPg1 wrt trap enb.              |

| 12  | HintEnb                | 4   | TxtPg2 wrt trap enb.              |

| 11  | SINGLESTEP mode        | 3   | AuxMem Text/Lores write trap enb. |

| 10  | XTRA BIT output to pin | 2   | Aux Mem Hires write trap enb.     |

| 9   | CA / PB1               | 1   | JoyStick access trap enable       |

| 8   | OA / PB0               | 0   | \$C8-Fxx trap enb.                |

|     |                        |     |                                   |

#### **NOTES:**

- 18. The OA/PB0 and CA/PB1 bits simulate presses on the Open-Apple and Closed-Apple keys (also joystick PB0 and PB1) when set to '1's. These values are 'OR'd with actual pushbutton presses if a joystick is connected to the Apple // Emulation Card game port.

- 19. All bits in the control register are 'active high' so that '1's in the register activate the corresponding descriptions above.

- 20. The high byte (Bits 8-15) are accessed at loc. B+xxx20. The low byte (Bits 0-7) are accessed at loc. B+xxx21.

- 21. Reading back from this location is supported to facilitate testing and simply returns the last value written.

#### 6.1.12 THE APPLE // CONTROL REGISTER

Read/Write Addr: \$C02B Size: 8-bits

The Apple // Control Register is accessable from the 65C02 and not the Macintosh. It provides some additional functional controls not available from the normal soft-switches. '1's in the register bits cause the following actions:

#### **BIT DESCRIPTION**

- 7 Output on SPARESSW pin from Gate-Array.

- Disable External ROM port access internal ROM space.

- 5 Enable Write to ROM areas if External ROM enabled.

- Enable Alternate 64K Aux Bank

- Enable Alternate DarkSide ROMbank

- Enable Hi Speed 2 MHz mode Per notes

- Head Select output for 3.5" disks goes high. 1

- SEL3.5 Dsk output goes high.

#### NOTES:

- 22. When bit 2 is set, The 65C02 will be run at 2 MHz most of the time, rather than the normal 1 MHz. It will be run at 1 MHz when the Mac or the internal memory refresher are requesting memory cycles; and when the Slot 6 Disk Motor-On switch at \$C0E8,9 is set and bit 0 - the 3.5" Disk select - is high.

- 23. The functions of Bits 3,4, and 5 are 'OR'ed with the corresponding function bits in the LC-Accessable Control registers.

NOTICE OF PROPRIETARY PROPERTY THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE FOLLOWING: (i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

SIZE

DRAWING NUMBER

343S0111-A

SCALE: NONE

SHT 20 OF 22

### 6.2 THE MACINTOSH INTERFACE:

Apple // Emulation Card is designed to interface easily to the LC and other Macintosh computers. It will generate an internal 'Select' signal in response to the following patterns on its address inputs:

When FC(0-2) = 0-6

| LC | FC3 | A31 | A27 | A26 | A25 | A24 | A23 | A22 | A21 | A20 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | 1   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | Χ   | X   |

| 1  | 0   | Χ   | Χ   | Χ   | Χ   | Χ   | 1   | 1   | 1   | 0   |

| 0  | Χ   | 1   | 1   | 0   | 1   | 1   | χ - | 1   | 1   | 1   |

When the 'Select' condition is satisfied and the Mac asserts  $\overline{AS}$ , the Apple // Emulation Card will generate a  $\overline{ROMSEL}$  and a  $\overline{DSACK0}$  about 210ns later if the  $\overline{CE}$  input is high, or allow access to the internal registers and eventually generate a  $\overline{DSACK1}$  if the  $\overline{CE}$  input is low and a valid register was accessed. If a valid register is not accessed  $\overline{DSACK1}$  will not be generated. The Base address referred to in the previous register descriptions consists of the select condition and the  $\overline{CE}$  input low when  $\overline{AS}$  is asserted. The main purpose of the  $\overline{CE}$  input is to provide support for an optional configuration ROM. If A19 is connected to the  $\overline{CE}$  pin, accesses to the upper half of the card's 1 Meg address space will cause a  $\overline{ROM}$  enable and a  $\overline{DSACK1}$ , and accesses to the lower half will enable the Apple // Emulation Card registers.

#### NOTE:

24. The time between AS input active and DSACKO or DSACK1 outputs active will vary depending on the type of access and the point in the 65C02 timing cycle where the access is requested.

Apple // Emulation Card does not use the Macintosh clock to develop its interface timing. Rather, the AS signal from the Macintosh is synchronized to the internal 14.31818MHz clock and this clock is used to generate the timing required. Accesses to internal registers and the 128K DRAM on the card also require additional time to come into sync with the 65C02 processor cycle.

This method of operation avoids any bus or timing conflicts between the 65C02 and the 680XX in the Macintosh, but results in an indeterminate number of wait states for any given Apple // Emulation Card access cycle. In general, ROM cycles will have at least 200ns of wait state before DSACKO is generated, and Register or RAM access cycles will have no more than 1 μs of wait states.

(i) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE (ii) NOT TO REPRODUCE OR COPY IT

(iii) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

- REFERENCES: The following is a list of all the pertinent ASIC deliverables filed in Document Control:

- Logic and pin-to-pin timing specifications for all LSI Logic macrocells and macrofunctions used in the Apple // Option Chip Gate-Array.

- 2. Functional and pin timing specifications for all compiled blocks such as ROM, RAM or PLA, in standard LSI Logic published format.

- 3. Two (2) magnetic tapes containing the schematic netlist file for those parts of the Apple // Option Chip Gate-Array that LSI Logic or Apple has sole ownership of and containing a list of those netfile names.

- 4. Logic diagram plot for those parts of the Apple // Option Chip Gate-Array which LSI Logic or Apple has sole ownership of and as supplied by Apple for those parts designed by Apple.

- 5. File of post-layout node and net capacitances and names for all circuit blocks that LSI Logic or Apple has sole ownership of.

- 6. Two (2) magnetic tapes of functional timing simulation inputs and outputs, including production test vectors, plus printed listing of file names.

- 7. Critical path timing analysis, including simulation results, if done by Apple and agreed by LSI Logic.

- 8. Two (2) database tapes for all mask layers created specifically for Apple, including cell interiors of those cells wherein LSI Logic of Apple has sole ownership, plus printed listing of file names.

- Name of manufacturer and complete model designation of target test hardware and two (2) copies of the magnetic tape and printed listing of competed test program (production version, object code), plus printed listing of file names.

- 10. Two (2) copies (magnetic tape) of any existing high-level language test program, supporting documentation and file listings.

- 11. Load board and load board documentation, including schematics, description, mechanical drawings and target test hardware designation.

- 12. Bonding diagram.

- 13. Twenty-five (25) prototype units of the product in conformance with post-layout timing simulation and the design database.

- 14. All material owned solely by LSI Logic required to perfect ownership of the Maskworks and other Inventions assigned to Apple under this Agreement, including but not limited to (i) the supply of deposit materials required to register a Mask Work under the Semiconductor Chip Protection Act of 1984, Public Law 98-620, Chapter 9 of Title 17, United States Code, and/or, (ii) the supply of deposit materials required for registration of copyrights under Title 17, United States Code.

NOTICE OF PROPRIETARY PROPERTY