## CORTLAND I/O Timing

# November 4, 1985

## Apple Computer, Inc. - CONFIDENTIAL

The Cortland computer has seven I/O slots that are almost identical to the slots in the Apple //e, the only exception being /M2SEL which replaces  $\mu$ PSYNC on pin 39. The slots behave like their counterparts in the //e with only a few differences, the most important one being the behavior of the address bus. Since the Cortland computer can operate at 2.8 MHz and has a 24-bit address, the address bus to the slots is not always valid as it was in the //e. The signal /M2SEL indicates when a valid address for banks 224/225 (hex \$E0/\$E1) is present on the address bus and so should be used to qualify any address decoding that does not use one of the I/O enable lines.

|                       | 26 | 25 | <b>E</b> 2. 4          |

|-----------------------|----|----|------------------------|

| GND                   |    |    | +5V                    |

| (NC on slot 1) DMA IN | 27 | 24 | DMA OUT (NC on slot 7) |

| (NC on slot 1) INT IN | 28 | 23 | INT OUT (NC on slot 7) |

| /NMI                  | 29 | 22 | /DMA                   |

| /IRQ                  | 30 | 21 | RDY                    |

| /RESET                | 31 | 20 | NOSTRB                 |

| ЛNH                   | 32 | 19 | NC                     |

| -12V                  | 33 | 18 | RW                     |

| -5V                   | 34 | 17 | A15                    |

| (CREF on sbt 7) NC    | 35 | 16 | A14                    |

| 7M                    | 36 | 15 | A13                    |

| <u>Q</u> 3            | 37 | 14 | A12                    |

| PH1                   | 38 | 13 | A11                    |

| M2SEL                 | 39 | 12 | A10                    |

| PHO                   | 40 | 11 | A9                     |

| /DEVSEL               | 41 | 10 | A8                     |

| D7                    | 42 | 9  | A7                     |

| D6                    | 43 | 8  | A6                     |

| D5                    | 44 | 7  | A5                     |

| D4                    | 45 | 6  | A4                     |

| D3                    | 46 | 5  | A3                     |

| D2                    | 47 | 4  | A2                     |

| D1                    | 48 | 3  | A1                     |

| DO                    | 49 | 2  | AO                     |

| +12V                  | 50 | 1  | NOSEL                  |

| 4124                  |    |    |                        |

Cortland I/O Slot Pinout

The total current available for the 7 slots is 500 mA at +5V, 250 mA at +12V, 200 mA at -5V, and 200 mA at -12V.

The support circuitry for the slots is designed to handle a DC load of 2 LS TTL loads and an AC load of no more than 15 pF per pin per slot.

Apple Computer, Inc.

Page 2

CONFIDENTIAL

Cortland I/O Timing

.

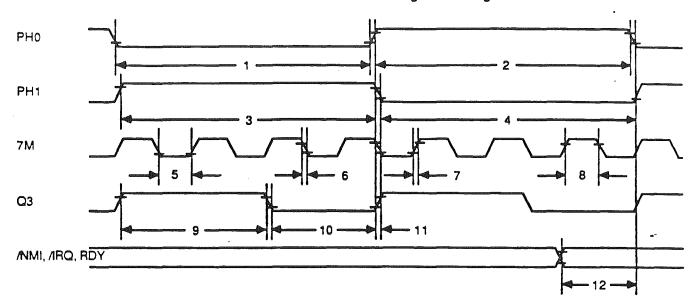

#### Slot I/O Clock and Control Signal Timing

| Number | Description                      | Min(ns) | Max(ns) |

|--------|----------------------------------|---------|---------|

|        | PH0 low time                     | 480     | ,       |

| 2      | PH0 high time                    | 480     |         |

| 3      | PH1 high time                    | 480     |         |

| 4      | PH1 low time                     | 480     |         |

| 5      | 7M low time                      | 60      |         |

|        | Fall time, all clocks            |         | 10      |

| 6<br>7 | Rise time, all clocks            |         | 10      |

| 8      | 7M high time                     | 60      |         |

| 9      | Q3 high time                     | 270     |         |

| 10     | Q3 low time                      | 200     |         |

| 11     | Skew, PH0 to other clock signals | -10     | 10      |

| 12     | Control signal setup time        | 140     |         |

All of the clock signals present on the I/O slots are buffered by a custom I.C. called the "Slot Maker". As a result these signals are delayed somewhat from the corresponding signals on the main board. All of the timing parameters given here and with the other diagrams have been adjusted to account for this delay.

Apple Computer, Inc.

CONFIDENTIAL

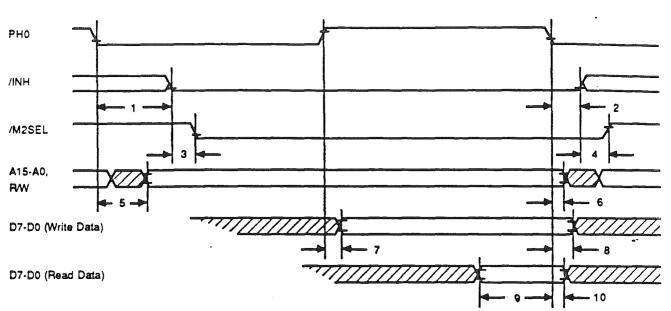

Slot I/O Read and Write Timing

| Number | Description                                           | Min(ns)                                                   | Ma |

|--------|-------------------------------------------------------|-----------------------------------------------------------|----|

| 4      | /M2SEL low from PH0 low                               | - 9, 0 # 0 <b>0 0 0 4 0 0 0 0 0 0 0 0</b> 0 0 0 0 0 0 0 0 | 1  |

| 2      | /M2SEL hold time                                      | -10                                                       |    |

| 3      | I/O enable low from PH0 high (/DEVn, /IOSELn, /IOSTRB | )                                                         |    |

| · 4    | I/O enable high from PH0 low (/DEVn, /IOSELn, /IOSTRB | ) 10                                                      |    |

| 5      | Address and R/W valid from PH0 low                    | -                                                         | 1  |

| 6      | Address and R/W hold time                             | 15                                                        |    |

| 7      | Write data valid delay                                |                                                           |    |

| 8      | Write data hold time                                  | . 30                                                      |    |

| 9      | Read data setup time to PH0                           | 140                                                       |    |

| 10     | Read data hold time                                   | 10                                                        |    |

The standard Cortland slot I/O timing is shown in the above diagram. When the computer is running in its high speed mode the address bus to the I/O slots is not valid entire PHO cycle, and therefore, cannot be used to perform unqualified address deconsignal /M2SEL, which replaces the signal  $\mu$ SYNC, indicates when a slow, synchronize cycle is taking place and also shows when the value on the address bus will remain valid current PHO cycle. This means that cards which use the Apple //e technique of "phantom put multiple I/O devices on one card must use /M2SEL to qualify their address decoding ci

Apple Computer, Inc.

#### Cortland I/O Timing

I/O Read and Write Timing with /INH Active

| Number | Description                        | Min(ns) | Max(ns) |

|--------|------------------------------------|---------|---------|

| 1      | /INH valid after PH0 low           | ,       | 175     |

| 2      | /INH hold time                     | 15      |         |

| 3      | /INH low to /M2SEL low delay       |         | 30      |

| 4      | /INH high to /M2SEL high delay     |         | 30      |

| 5      | Address and R/W valid from PH0 low |         | 100     |

| 6      | Address and R/W hold time          | 15      |         |

| 7      | Write data valid delay             |         | 30      |

| 8      | Write data hold time               | 30      |         |

| 9      | Read data setup time to PH0        | 140     |         |

| 10     | Read data hold time                | 10      |         |

Read and write cycles that are directed to the I/O slots by /INH have the same timing parameters as normal I/O reads and writes. When /INH is asserted, the computer responds as if a MEGA // memory cycle were being performed.

Cards that use the /INH signal will only function properly if the computer is running in its slow mode (1 MHz). If the computer is running in its high speed mode, the addresses that are seen by cards in the I/O slots are not guaranteed to be valid during an entire PH0 cycle. Also, since the upper 8 bits of the memory address are not available to cards, the usefulness of /INH is greatly reduced in this machine.

Apple Computer, Inc.

CONFIDENTIAL

November 4, 1985

Cortland I/O Timing

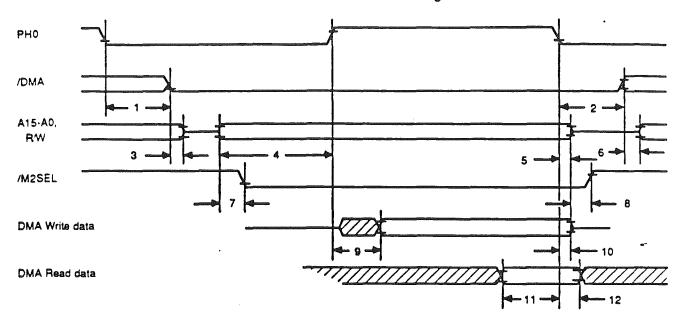

/DMA Read and Write Timing

| Number | Description                               | Min(ns)                                                    | Max(ns) |

|--------|-------------------------------------------|------------------------------------------------------------|---------|

| 4      | /DMA low from PH0 low                     | 3 8 <del>8 6</del> 9 7 7 8 8 8 8 8 9 8 9 7 8 7 8 7 8 7 8 7 | 120     |

| 2      | /DMA high from PH0 low                    |                                                            | 120     |

| 3      | A15-A0 and R/W float from /DMA            |                                                            | 30      |

| 4      | DMA address and R/W valid before PH0 high | 300                                                        |         |

| 5      | DMA address and R/W hold time             | 10                                                         |         |

| 6      | /DMA high to A15-A0 and R/W active        |                                                            | 30      |

| 7      | DMA address valid to /M2SEL low           |                                                            | 30      |

| 8      | DMA address float to /M2SEL high          |                                                            | 30      |

| 9      | PH0 high to write data valid              |                                                            | 100     |

| 10     | DMA write data hold time                  | 10                                                         |         |

| 11     | DMA read data setup time                  | 125                                                        |         |

| 12     | DMA read data hold time                   | 30                                                         |         |

DMA devices will work if the Cortland computer is running slow, at 1 MHz. If the computer is running in its high-speed mode, at 2.8 MHz, DMA will work to the high-speed memory (banks 0 - 127) and will not work with the slow part of the system (all I/O and video memory). DMA can be performed to or from any part of the Cortland memory map, provided that the DMA Bank Register in the FPI is first set to the correct bank.

Apple Computer, Inc.

CONFIDENTIAL